# MJ105 (SILICON) BU105

## HORIZONTAL DEFLECTION SILICON TRANSISTORS

$\dots$  designed for use in line operated black and white (19 and 20 inch  $110^{\rm O}$  deflection circuits) or color (11 and 14 inch  $90^{\rm O}$  deflection circuits) television receivers.

- High Collector-Emitter Voltage –

VCER (Peak) = 1400 Vdc MJ105

= 1500 Vdc BU105

- Collector-Emitter Saturation Voltage —

VCE(sat) = 5.0 Vdc (Max) @ IC = 2.5 Adc

- Fall Time @ I<sub>C</sub> = 2.0 Adc t<sub>f</sub> = 0.5 μs (Typ) = 1.0 μs (Max)

#### MAXIMUM RATINGS

| Rating                                                                | Symbol                           | MJ105       | BU105       | Unit                       |

|-----------------------------------------------------------------------|----------------------------------|-------------|-------------|----------------------------|

| Collector-Emitter Voltage                                             | VCEO                             | 750         |             | Vdc                        |

| Collector-Emitter Voltage — Continuous (RBE = 100 Ω) Peak             | VCER                             | 750<br>1400 | 750<br>1500 | ٧                          |

| Collector-Base Voltage — Continuous<br>Peak                           | VCB                              | 750<br>1400 | 750<br>1500 | ٧                          |

| Emitter-Base Voltage                                                  | VEB                              | 5.0         |             | Vdc                        |

| Collector Current - Continuous                                        | ¹c                               | 25          |             | Adc                        |

| Base Current — Positive<br>Negative                                   | 1B                               | 25<br>15    |             | Adc                        |

| Total Device Dissipation @ T <sub>C</sub> = 90°C<br>Derate above 90°C | PD                               | 10<br>0.4   |             | Watts<br>W/ <sup>O</sup> C |

| Operating and Storage Junction Temperature<br>Range                   | T <sub>J</sub> ,T <sub>stg</sub> | -65 to +115 |             | °C                         |

#### THERMAL CHARACTERISTICS

| Characteristic                       | Symbol | Max | Unit<br>OC/W |  |

|--------------------------------------|--------|-----|--------------|--|

| Thermal Resistance, Junction to Case | ⊕1C    | 2.5 |              |  |

#### ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                                                                | Symbol     | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|------|

| OFF CHARACTERISTICS                                                                                                                                                           |            |     |     |     |      |

| Collector-Emitter Sustaining Voltage (1)<br>(I <sub>C</sub> = 100 mAdc, I <sub>B</sub> = 0)                                                                                   | BVCEO(sus) | 750 | -   | -   | Vdc  |

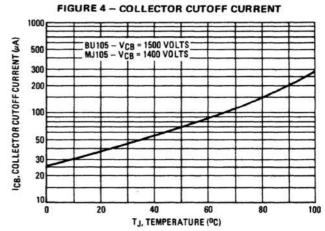

| Collector Cutoff Current<br>(VCE = 1400 Vdc, VBE = 0) MJ105                                                                                                                   | CES        | -   | -   | 1.0 | mAdd |

| (V <sub>CE</sub> = 1500 Vdc, V <sub>BE</sub> = 0) BU105                                                                                                                       | i 1        | -   | -   | 10  |      |

| Emitter-Base Voltage<br>(I <sub>E</sub> = 100 mAdc, I <sub>C</sub> = 0)                                                                                                       | BVEBO      | 5.0 | -   | -   | Vdc  |

| ON CHARACTERISTICS                                                                                                                                                            |            |     |     | -   |      |

| Collector-Emitter Saturation Voltage<br>(I <sub>C</sub> = 2.5 Adc, I <sub>B</sub> = 1.5 Adc)                                                                                  | VCE(sat)   | -   | -   | 50  | Vdc  |

| Base-Emitter Saturation Voltage<br>(IC = 2.5 Adc, IB = 1.5 Adc)                                                                                                               | VBE(sat)   | -   | -   | 1.5 | Vdc  |

| DYNAMIC CHARACTERISTICS                                                                                                                                                       | •          |     |     |     |      |

| Current-Gain—Bandwidth Product (2)<br>(IC = 0 1 Adc, VCE = 5.0 Vdc, f <sub>test</sub> = 1.0 MHz)                                                                              | fŢ         | -   | 7.5 | -   | MHz  |

| Output Capacitance<br>(VCB = 10 Vdc, IE = 0, f = 0 1 MHz)                                                                                                                     | Cob        | -   | 65  | -   | pF   |

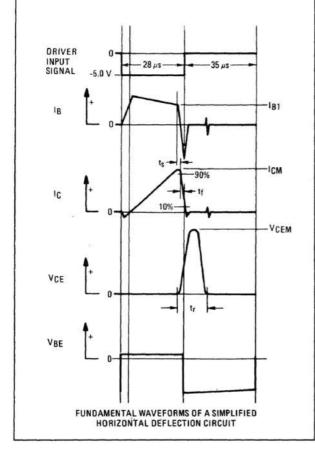

| SWITCHING CHARACTERISTICS (Figure 1 and                                                                                                                                       | text)      |     |     |     |      |

| Fall Time<br>(I <sub>C</sub> = 2.0 Adc, I <sub>B1</sub> = 1.5 Adc, L <sub>B</sub> = 12 µH,<br>R <sub>B</sub> = 2.5, Non-optimum values to comply<br>with BU105 specification) | tę         | -   | 05  | 1.0 | μs   |

(1) Pulse Test: Pulse Width 300 µs, Duty Cycle ≈ 2.0%...

(2) fT = |hfe| • ftest

2.5 AMPERE

POWER TRANSISTORS

NPN SILICON

1400, 1500 VOLTS

10 WATTS

#### CIRCUIT OPTIMIZATION

Test/application circuit and operating waveforms for 8U105/MJ105 are shown in Figure 1. It may be used to evaluate devices in the conventional manner, i.e., to measure fall time, storage time, and saturation voltage. However, the circuit was designed with operating efficiency in mind, so that it could be used to evaluate devices by one simple criterion, supply power input. Excessive power input

can be caused by a variety of problems, but it is the dissipation itself that is of fundamental importance. Once the transistor operating point has been established, fixed circuit values may be selected for the test fixture. Factory testing may then be made with one meter reading, without adjustment of the test apparatus.

#### FIGURE 1 - TEST CIRCUIT AND WAVEFORMS O + 50 Vdc 1.8 k 0.005 µF MPSU03 CR 1.0 µF 0.0063 uF HP214A T1 -1.5 kV (See Waveform) μF MR2268 200 1.0 uF ≥ 180 ≥51 Vdc BU105 600 Vdc MJ105 PIN 10 "F 25 Vdc 120 Vdc O BASE CIRCUIT VALUES Wattmeter LB

### Switching Test 2.5 12.0 Optimum 7.0 15.0

#### **DESCRIPTION OF SPECIAL COMPONENTS**

#### DUMMY YOKE INDUCTOR (LY)

2.0 mH, 52.5 turns, #16 AWG enamel wire 15 turns per layer, 3.5 layers on 1.375 inch diameter bobbin, enclosed in a Ferroxcube, cup core K535221-B2A, with a 0.687 inch diameter core, with 0.003 inch core gap. Use a nylon bolt and nut to hold cup halves together.

## DUMMY HIGH VOLTAGE AND HORIZONTAL SCAN TRANSFORMER (LF)

5.5 mH, 121 turns, #20 AWG enamel wire 33 turns per layer, 3.6 layers 1 mil mylar insulation between layers wound on 1 leg of Allen Bradley 0.5 inch square Ferrite "U" core (2) WO3 material with 0.007 inch gap in each leg. Core halves held together with plastic.

#### **DRIVER TRANSFORMER (T1)**

Motorola part number 25D68782A05-1/4" laminate "E" iron core. Primary Inductance - 39 mH, Secondary Inductance - 0.22 mH, Leakage inductance with primary shorted - 2.0  $\mu$ H. Primary 260 turns, #28 AWG enamel wire, Secondary 17 turns, #22 AWG enamel wire.

#### BASIC CONSIDERATIONS

The primary consideration when choosing a deflection transistor for a conventional (parallel connected) circuit, as shown in Figure 1, is one of voltage capability. The flyback voltage to which the device will be subjected is a relatively predictable value with respect to the main power supply voltage. This voltage pulse, shown in Figure 1, will usually be about 8 times the value of V<sup>+</sup>, but may be varied somewhat by adjusting retrace time and flyback tuning. For this reason these high voltage devices are particularly useful in cost conscious solid state receivers, as they permit the use of an off-the-line half wave power supply.

#### **COLLECTOR CIRCUIT VALUES**

The power supply used in the circuit of Figure 1, was chosen to produce a 1000 volt collector pulse on the transistor, a conservative value, recommended for unregulated applications. The values of yoke (Ly), flyback primary (LF), retrace capacitor (CR), and "S" shaping capacitor (CS) shown, will result in a peak collector current of about 2.0 A. This is sufficient to deflect (and provide high voltage for) large screen  $110^{\rm O}$  black and white or small  $90^{\rm O}$  color receivers. Peak collector currents to 2.5 A may be handled by the BU105/MJ105. Holding the supply constant for most efficient application, adjustment of amount of deflection may be made by raising or lowering Ly and LF. Remember that Ly Iy is constant for the fixed voltage situation, and actual deflection is proportional to Iy  $\sqrt{\text{Ly}}$ . Values of CS and CR must be varied inversely with Ly to maintain retrace and "S" shaping periods.

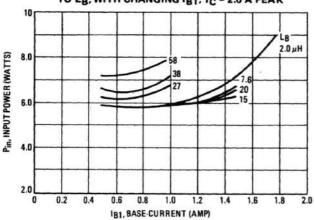

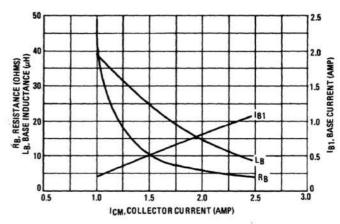

FIGURE 2 — RELATIONSHIP OF POWER DISSIPATION TO LB, WITH CHANGING IB1, IC = 2.0 A PEAK

#### **BASE CIRCUIT VALUES**

The driver power supply and driver transistor type can be selected according to convenience. A TO-5 or Uniwatt type will generally be needed. Once this is done, the turns ratio of the driver transformer can be picked to produce about 4 to 5 volts peak to peak at the base of the output device. Tight coupling between windings is recommended on early designs to allow optimizing leakage inductance by adding inductance externally. Later, the leakage can be "designed in" to the transformer. The RB and its bypass electrolytic, often called the "speed up" circuit, allows adjustment of IB1 (or IB "end of scan" or IB end) while still providing a low ac impedance for good turn-off of the output device. In Figure 2, the effects of varying LB and IB1 on the total power input to the deflection circuit are shown. Note that an optimum LB can be found which will produce low dissipation over a wide range of IB1. This is desirable in order to produce efficient operation over a wide range of circuit component tolerances. Likewise, best LB also gives the least sensitivity to output transistor hee.

The best value of LB found in Figure 2 is 15  $\mu$ H. Remember that this is the sum of the actual leakage inductance of the transformer (secondary inductance with primary shorted) and an external L, if necessary. The best value of IB1 is 0.8 A achieved in the typical device by using RB = 7  $\Omega$ , derived experimentally.

These are the choices recommended for the test fixture, when the transistor is used at  $I_{CM} = 2.0 \, A$ . For other values of  $I_{CM}$  the drive circuit components must be changed. Figure 3 shows the values of LB and  $I_{B1}$  which should be used.

The value of R<sub>B</sub> which will be required to produce the I<sub>B1</sub> is also given, but of course, it is not an independent variable.

#### PERFORMANCE

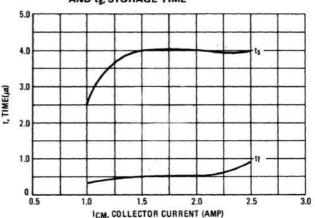

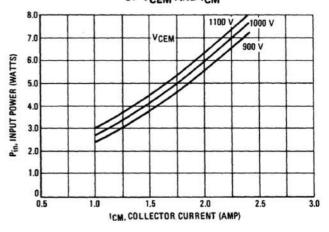

Shown in Figures 4 and 5 are the results which will be typically obtained with the test circuit at various operating conditions.

FIGURE 3 - INTERRELATION OF RB, LB, AND IB1

FIGURE 4 – INTERRELATION OF tf, FALL TIME AND ts, STORAGE TIME

FIGURE 5 - PIN. POWER DISSIPATION, WITH DEVIATIONS OF VCEM AND ICM

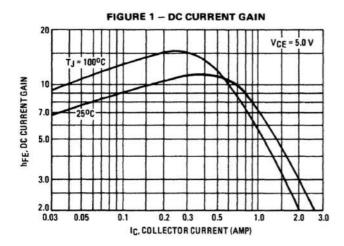

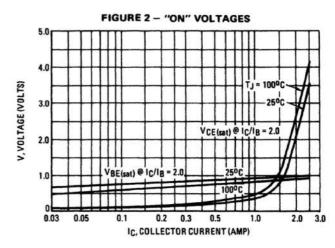

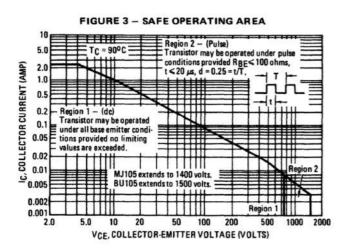

#### TYPICAL TRANSISTOR CHARACTERISTICS